集微网消息,3月29日,台积电董事长刘德音及台积电首席科学家H.-S Philip Wong在IEEE网站上发表了一篇名为《How We'll Reach a 1 Trillion Transistor GPU》的文章,讲述了台积电是如何达成1万亿晶体管芯片的目标。

文章指出,从1997年击败国际象棋人类冠军的IBM深蓝超级计算机,到2023年爆火的ChatGPT,再过15年,人工智能(AI)将发展到可以“合成知识”(synthesize knowledge)的地步,可以创作诗歌、编写总结报告和计算机代码,甚至可以设计集成电路。

所有这些奇妙的人工智能应用都归功于三个因素:高效机器学习算法的创新、训练神经网络的大量数据的可用性,以及通过半导体技术的进步实现节能计算的进步。

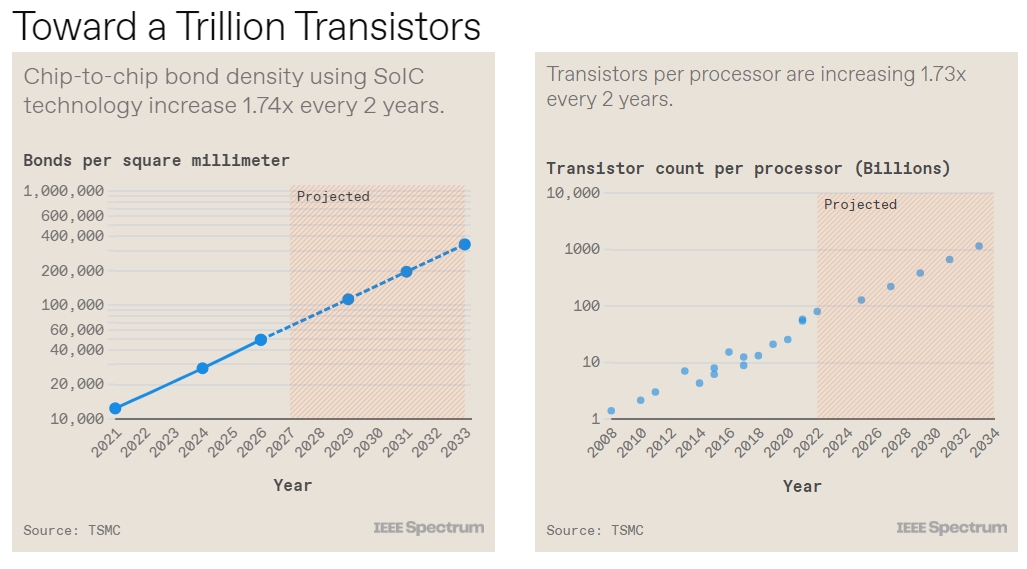

文章内容称,如果AI要以目前的速度发展下去,它将需要半导体产业做出更多贡献。10年内,它将需要1个1万亿晶体管的GPU,也就是说,GPU的设备数量是当今典型设备数量的10倍。

文章称,CoWoS是台积电的硅晶圆上芯片先进封装技术,目前已在产品中得到应用。示例包括英伟达Ampere和Hopper GPU。Ampere有540亿个晶体管,Hopper有800亿个。从7 nm技术到更密集的4nm技术的转变使得在基本相同的面积上封装的晶体管数量增加了50%。Ampere和Hopper是当今大型语言模型 ( LLM ) 训练的主力,训练ChatGPT需要数万个这样的处理器。

HBM是对AI日益重要的另一项关键半导体技术的一个例子,通过将芯片堆叠在一起来整合系统的能力,台积电称之为SoIC(system-on-integrated-chips)。

文章预测,10年内,多芯片GPU将拥有超过1万亿个晶体管。

文章结论认为,在智能时代,半导体技术是人工智能新能力和应用的关键推动者。新的GPU不再受过去的标准尺寸和外形尺寸的限制。新的半导体技术不再局限于在二维平面上缩小下一代晶体管。整合人工智能系统可以由尽可能多的节能晶体管、用于专门计算工作负载的高效系统架构以及软件和硬件之间的最佳化关系组成。

(校对/刘昕炜)

登录

登录