2025集成电路发展论坛(成渝)暨三十一届集成电路设计业展览会(ICCAD-Expo 2025)上周举行。芯和半导体 CEO 兼总裁代文亮博士出席高峰论坛,在主旨演讲《集成系统 EDA 加速 AI 时代Chiplet 生态构建》中,详细介绍了在AI时代背景下、“从芯片到系统”的设计趋势,以及EDA工具及设计范式将会面临的机遇与挑战。

AI 时代主角,从“芯片—系统”

代文亮指出,在由 AI 推动的第四次工业革命背景下,AI计算正在逼近一个系统级奇点:计算边界从芯片内部,延伸至整个 AI 基础设施系统与互联网络中。单纯依赖芯片工艺或局部架构优化,已难以支撑算力的指数级增长。必须依赖算力、互联、存储与封装等多个维度开展系统层面的协同创新,才能实现算力指数级提升。设计优化也需从工艺协同(DTCO)转向系统架构协同(STCO),实现更全面的体系化联动。

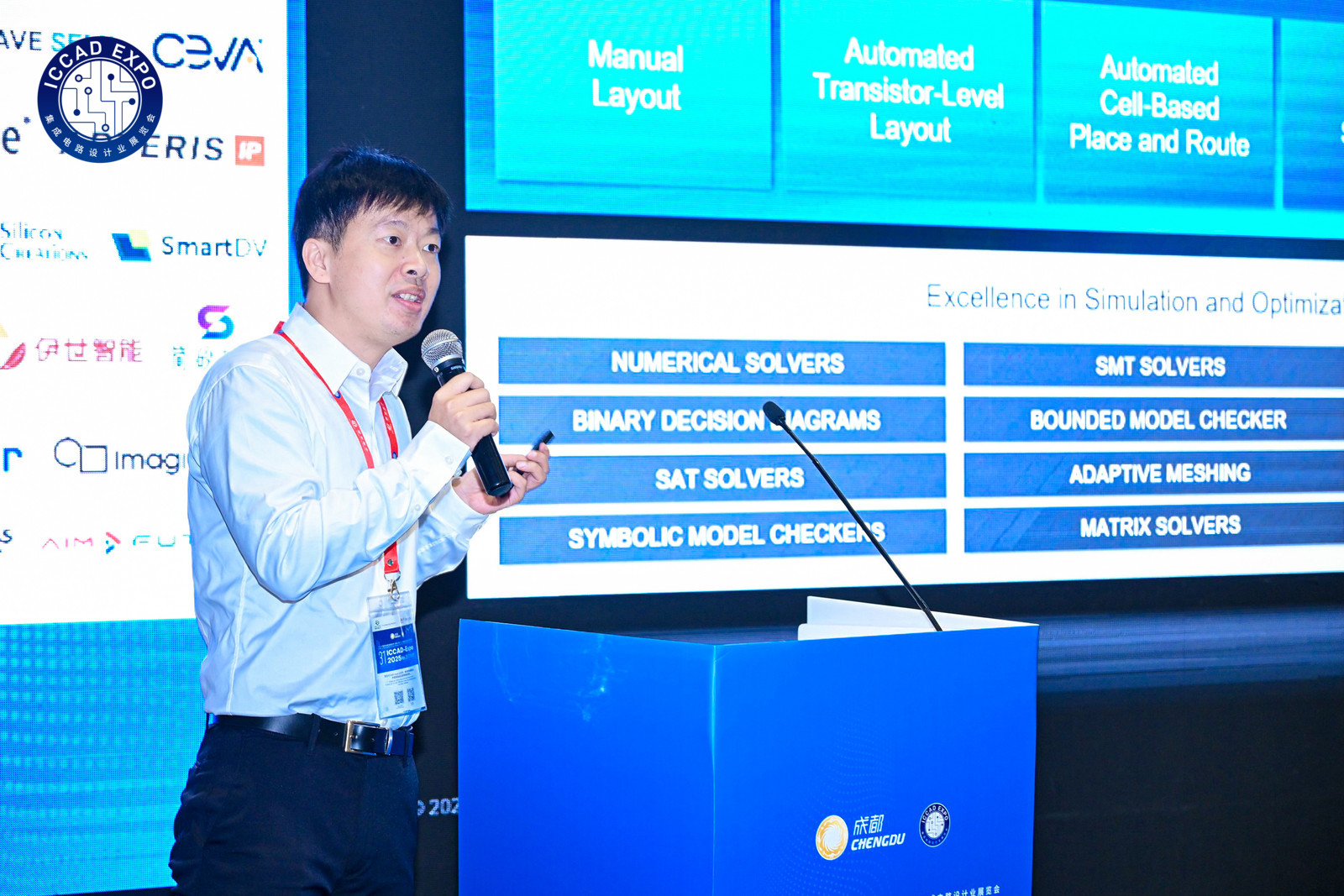

在芯片层面,Chiplet 和先进封装技术的全面落地,倒逼 EDA 工具从单芯片设计拓展至封装级协同优化;系统层面,从数据中心超节点到集群,设计对象已演变为涵盖异构算力、高速互联、供电冷却以及电源网络等在内的大型系统工程。EDA也需要同步升级,将设计范式从 DTCO 进一步拓展至全链路的 STCO,以支持“从芯片到系统”的设计能力跃迁。

为应对这一趋势,国际EDA 厂商近年来持续通过收购加速系统化转型。芯和半导体作为国内EDA代表企业,也在这一方向上积极布局,2025 年,芯和开启“为 AI 而生”战略,围绕“EDA for AI” 与 “AI+EDA” 双线全面推进。

EDA FOR AI:凭借在 Chiplet、先进封装与系统设计领域的长期技术积累,以及多物理场仿真分析方面的基础能力,芯和近年来在“从芯片到系统全栈 EDA”方向形成了先发布局优势。目前,其技术可全面覆盖 AI 算力芯片、AI 节点的纵向扩展(Scale-Up)以及 AI 集群的横向扩展(Scale-Out),保障AI 算力稳定输出。

借力 AI,成就更好的 AI

代文亮表示,AI 对 EDA 的影响已在行业内逐步显现。芯和“EDA+AI”的布局,基于自研“XAI 智能辅助设计” 核心底座,将四个智能体融入 EDA 流程中,从建模、设计、仿真、优化等多方面赋能,推动 EDA 从传统 “规则驱动设计” 演进为 “数据驱动设计”。

建模方面,传统 EDA 高精度仿真非常耗时。芯和通过将神经网络、生成对抗网络等 AI 算法与多物理场仿真工具结合,可加速常用器件的建模、校准和验证。相关模型覆盖先进工艺节点(包括 PDK、3DIC TSV、DTC)、封装与PCB板材、器件模块(功率器件、射频模组)及接口与互连(高速 I/O 接口、线缆、天线)。代文亮补充,AI 模型的预测能力不仅提升仿真效率和精度,也有助于减少对企业关键设计参数的暴露,从而提升知识产权保护水平。

在仿真预测方面,随着设计对象从芯片扩展至系统级,多物理场仿真的重要性显著提升。芯和基于自研的“场—路—热—应力—流体”多物理场仿真引擎构建了“仿真预测智能体”,覆盖芯片、3DIC、封装、板级到综合系统的设计流程,能够对电流、电压、温升、电场、磁场、流场、应力场等关键指标进行快速预测,缩短设计到量产的周期。同时,其大规模参数空间探索能力,旨在帮助设计团队在多变量组合中更快速地找到可行的优化方向,推动异构集成系统从“规则驱动”向“数据智能驱动”发展。

代文亮补充,AI赋能的另一大优势在于持续的学习能力。通过与产业伙伴在 Chiplet、先进封装与系统设计等场景下的合作,芯和的AI +EDA不断吸收新的数据、参数特征与工程经验,形成持续迭代的学习机制,为 EDA 工具优化提供长期支撑。让EDA从“被动工具”成长为“主动的协同者”。

最后,关于近期被广泛讨论的“物理人工智能”,代文亮分享道,“物理人工智能”时代的临近,将为“系统化设计”孕育更为广阔的市场空间。物理人工智能天然涉及跨多物理系统属性,设计工作将更依赖系统级的整体视角,这也将成为芯和半导体兑现“多物理仿真引擎技术”技术潜力的更大舞台。代文亮表示,期待由 AI 驱动的设计、验证、仿真与系统协同,在物理 AI 的发展进程中释放更多潜能。