近日,南京航空航天大学集成电路学院、空天集成电路与微系统工信部重点实验室EICAS课题组在面向格基后量子密码芯片设计方向取得进展,对基于RRAM-CIM的高能效NTT加速器展开硬件实现和性能评估。相关研究成果以《DRR-NTT: Efficient NTT Accelerator in Lattice-Based Cryptography By Dimensionality Reduction in RRAM》为题被IACR The Workshop on Cryptographic Hardware and Embedded Systems (CHES) 2026录用。论文由南京航空航天大学陈洋(硕士研究生)、王辈、韩丽霞、吕飞、崔益军、王成华、刘伟强老师与英国贝尔法斯特女王大学博士后倪子颖合作完成。南京航空航天大学集成电路学院是该论文的第一作者和通信作者单位。

AI的广泛应用正使传统计算架构的“内存墙”问题日益凸显,数据频繁搬运已成为制约算力与能效的主要瓶颈。存算一体(CIM)架构通过将计算嵌入存储单元,为高效处理数据密集型任务提供了突破性路径。与此同时,量子计算的快速发展对现有公钥密码体系构成了根本性威胁。基于格困难问题的后量子密码(PQC)学成为构建量子安全体系的核心。值得注意的是,PQC系统的核心运算高度依赖于多项式乘法的高效实现,该过程通常由数论变换(NTT)完成,是影响系统性能的关键瓶颈。因此,实现高性能、高精度且能效优异的NTT硬件加速器,已成为推动下一代人工智能与密码学共同发展的关键挑战。

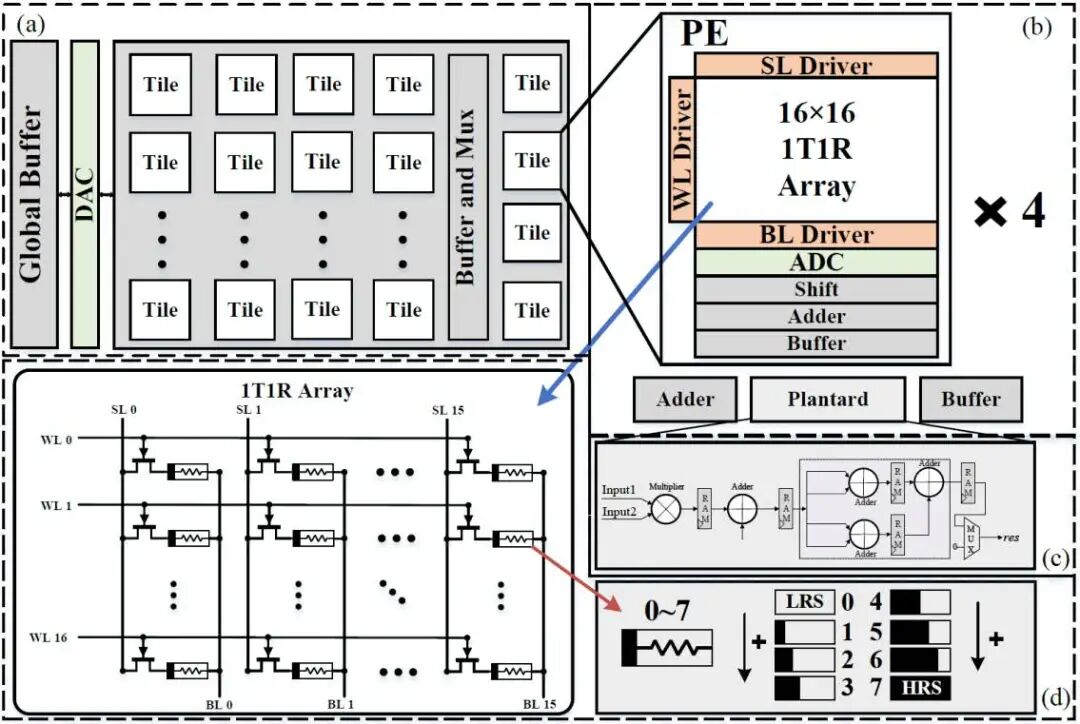

图1 DRR-NTT整体架构

针对上述挑战,研究团队提出了一种面向LB-PQC的基于RRAM-CIM的高能效NTT加速器——DRR-NTT。在阵列构造层面,采用矩阵降维方法,构建了迄今最小单元的RRAM-NTT计算阵列,不仅显著降低系统延迟,也有效抑制了阵列内部的列间干扰,且具备良好的可扩展性,可支持任意点数的NTT运算。

在映射与精度层面,创新性地引入3位权重映射方案,提高了阵列利用效率与信息存储密度,并首次结合真实RRAM器件的实测电阻数据进行量化误差分析,在同等条件下将计算误差控制在10-6量级。

在算法优化层面,首次将Plantard模乘算法适配于RRAM-CIM架构,显著简化了NTT中的模约简操作,降低了对预计算旋转因子矩阵的存储与管理开销,从而进一步减少了功耗与硬件资源消耗。这些创新共同构成了一套面向LB-PQC中NTT的高性能、高可靠硬件加速解决方案。

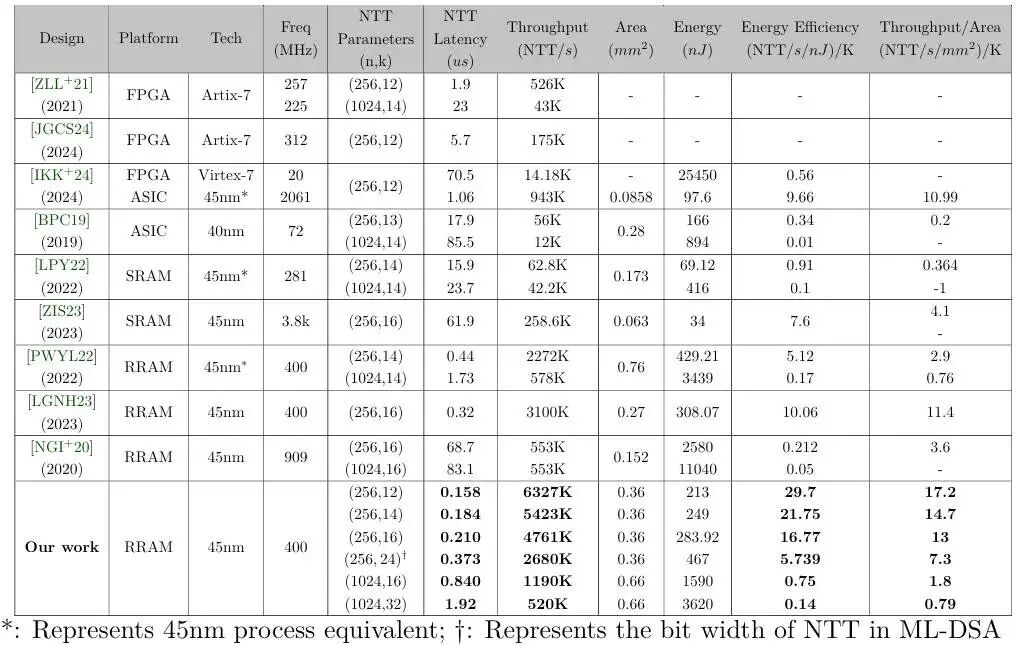

图2 DRR-NTT与最先进NTT加速器的性能比较

实验结果表明,在保证完整计算精度的基础上,该设计在架构层面实现了能效、吞吐与面积效率的协同优化,相比现有先进方案,吞吐提升达1.5至2.47倍,能效提升达1.6至4.25倍,单位面积吞吐亦提升超过1.5倍。同时所提出的NTT加速器可作为共享协处理器实例化于PQC和FHE架构中,由ML-KEM和ML-DSA的密钥生成、封装/解封装、签名及验证例程调用,并通过简单加载方案特定参数和旋转因子表,在FHE的密文乘法、密钥交换和自举过程中复用正向/逆向NTT运算。

CHES创立于1999年,是密码硬件与软件实现设计和分析研究领域的顶级学术会议。作为国际密码学研究协会(IACR)的专题会议,CHES搭建起密码学界与工程界的桥梁,吸引来自学术界、工业界、政府部门等各领域的参与者。CHES 2026会议将于2026年10月11日至15日在土耳其安塔利亚举行,所有录用论文将同时在IACR Transactions on Cryptographic Hardware and Embedded Systems期刊上发表。