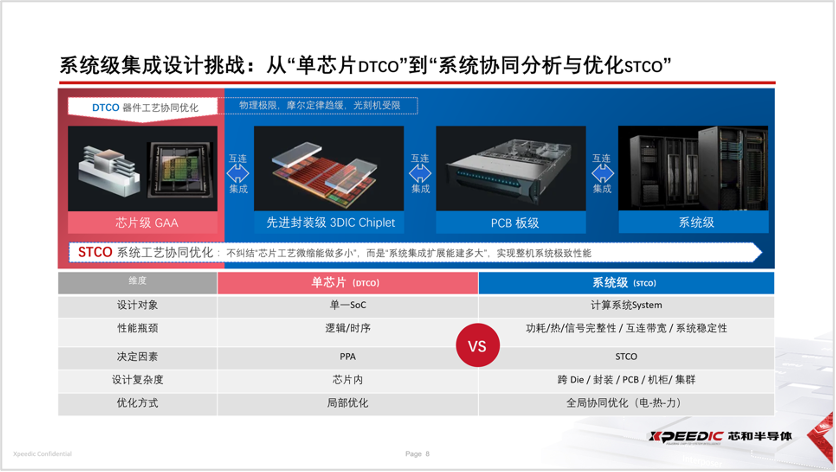

过去六十年,半导体行业习惯了摩尔定律的馈赠,相信只要制程微缩,算力就会无限增长。然而,面对AI大模型带来的指数级算力需求,传统的“单芯片先进制程”路径(DTCO)已触及物理与经济的极限。行业的竞争制高点,不可逆转地从单芯片性能最优,转向了系统级集成与优化。

在GTC 2026期间,英伟达创始人黄仁勋与知名科技博主Lex Fridman的一场深度对谈,为这场变革定下了基调。黄仁勋在访谈中高达12 次强调“极限协同设计(Extreme Co‑design)”,将其定义为AI算力时代的核心生存法则。他直言,AI计算已从“检索时代”的静态数据仓库,进化为“生成式AI时代”的Token生产工厂,硬件架构必须从单点芯片突破,转向芯片—封装—系统—数据中心的全栈协同,任何1%的环节不协同,都可能引发万卡集群效率指数级崩塌。这场由AI算力引爆的产业革命,正彻底改写半导体行业底层逻辑,也为深陷制程瓶颈、寻求突围的国产EDA,打开了一扇通往系统级创新的全新大门。

就在GTC大会落幕不久,SEMICON China 2026期间,国内系统级EDA领军企业芯和半导体召开16周年里程碑式品牌升级发布会,正式宣告从传统EDA工具软件商,转型为“AI时代的系统设计领航员”,以STCO(系统技术协同优化)方法论,重构从芯片到系统的智能设计全流程。

算力革命倒逼设计变革:从DTCO到STCO,EDA迎来生死抉择

过去六十年,半导体行业始终沿着摩尔定律的轨迹前行,DTCO(设计—工艺协同优化)是贯穿始终的核心逻辑。行业坚信,只要持续推进制程微缩,从28nm到7nm、3nm乃至2nm,晶体管密度提升就能带来算力增长,EDA工具也围绕单芯片内部逻辑与物理设计深耕,将封装、板卡、整机视为设计之外的“理想黑盒”。但AI大模型的爆发,彻底击碎了这一传统路径。

黄仁勋在GTC 2026上公布一组震撼数据:从ChatGPT问世到通用AI爆发,算力需求增长100倍;从通用AI迈向物理AI,算力将再增100倍。万亿参数大模型、自动驾驶域控制器、AI服务器集群、具身智能硬件,对算力、带宽、功耗、散热提出了远超单芯片承载能力的极致要求,单芯片物理极限已成为无法逾越的鸿沟 —— 功耗墙、散热墙、良率墙三重枷锁缠身,先进制程研发成本呈指数级飙升,流片失败动辄造成数千万美元损失,摩尔定律已逼近物理与经济的双重天花板。

更严峻的是,传统单芯片EDA的局限性,在AI时代已演变为“系统性灾难风险”。芯和半导体董事长凌峰博士在品牌发布会上直言:“现在客户面临的不是效率问题,而是生存问题。散热不周导致整机翘曲、电源网络缺陷引发封装熔断、系统级信号失效让流片报废,这些都是致命打击”。传统EDA仅关注晶粒(Die)内部设计,割裂芯片、封装、板级、整机的设计链路,电磁、热、应力等物理场分开仿真,忽略彼此强耦合效应,无法预判芯片在真实系统中的表现,最终陷入芯片级仿真完美,系统级运行崩溃”的困境。

与此同时,AI硬件架构迎来颠覆性变革,Chiplet异构集成、2.5D/3D先进封装、超高速互连、液冷散热、机柜级集群成为行业主流方向。英伟达推出的NVL72系统,将72颗Blackwell GPU互联为完整计算域,设计目标从孤立硅片转向整个机柜;国内厂商打造的 384 超节点集群,系统复杂度已超越国际同类产品。这种从“单芯片”到“多芯粒”再到“集群级超节点”的演进,让芯片与封装、PCB、机架的边界彻底模糊,原本可掩盖的信号抖动、散热不均、电压降问题,在系统尺度下被无限放大,成为决定产品成败的核心因素。

产业变革的方向已然清晰:半导体竞争制高点,已不可逆地从“单芯片性能最优”转向“系统级集成与优化”;EDA行业的核心范式,必须从依赖制程微缩的DTCO,升级为全链路协同的STCO。黄仁勋反复强调的“极限协同”,本质是对系统级全栈优化的极致追求;而芯和半导体提出的STCO,正是实现这种极限协同的EDA底层方法论,二者形成的产业共识,共同指向AI时代半导体设计的唯一破局之路。

STCO范式转移:芯和打破边界,重构AI时代设计逻辑

面对这种从微米级跨越到数据中心级的风险量级,传统的“先流片后验证”模式已经彻底失效。行业亟需一种能够跨越芯片、封装与系统的全栈EDA平台,在芯片生产之前,就精准预判并消除那些足以让系统崩溃的1%隐患。芯和半导体的品牌升级,正是基于对这一趋势的深刻洞察。面对从DTCO到STCO的行业巨变,芯和半导体基于16年技术沉淀提出的“重构芯片到系统的智能设计”,具体体现在三大维度的范式转移上。

第一个维度是边界的突破,从“单一芯片”走向“完整系统”打破物理边界桎梏。

传统单芯片EDA的边界狭窄,仅关注Die内部的逻辑与物理设计,将封装、板卡和整机视为“黑盒”,这导致“芯片级仿真完美,系统级运行崩溃”的窘境频发。通过STCO方法论,芯和实现了从IC到封装、板级、整机的端到端协同设计,直接在真实系统架构中进行场景化验证,凌峰博士强调:“我们不再追求单点性能极致,而是寻求系统整体性能、功耗与成本的全局最优解。这不是简单的设计范围拓展,而是设计思维的底层颠覆”。

芯和总裁代文亮博士指出,芯和的服务边界已彻底打破。任何围绕先进封装、异构集成、高带宽存储、超高速互连、高效电源网络及AI数据中心架构的客户,都是其核心腹地,市场天花板不再受限于芯片种类,而是随AI系统复杂度指数级扩张,真正适配AI算力时代的产业需求。

第二个维度是价值的跃迁,从加速设计到系统协同,将风险消除在设计阶段。

如果说传统EDA工具是在“加速”设计流程,那么芯和正在“重构”设计的底层逻辑。代文亮将其价值概括为:“我们不再只是让设计跑得更快,我们是让设计第一次就做对。通过STCO方法论,我们将试错成本从昂贵的产线转移至虚拟空间,帮助客户显著缩短上市时间,避免数百万美元的返工损失。这种‘避险价值’在AI军备竞赛中具有极高的溢价能力。”

芯和独有的多物理场耦合仿真引擎,能够实时计算电磁-热-应力的相互影响,精准捕捉芯片翘曲、封装熔断、信号完整性恶化等致命问题。通过系统级协同优化,帮助客户大幅缩短上市时间,彻底规避系统不匹配导致的灾难性返工,这不仅是效率的提升,更是研发确定性与安全性的保障。目前,芯和已构建起覆盖电磁、热、应力、流体、电源等多维度的仿真体系,拥有XStructure、XCFD、XStress、XET等20余款核心工具,形成完整的多物理场仿真矩阵,可支撑从芯片到集群的全尺度系统级分析,对标国际顶尖EDA巨头。

第三个维度是生态的整合,从“软件工具商”走向“生态平台制定者”

芯和STCO推动企业完成身份重塑,从单一工具供应商进化为生态系统构建者与行业范式制定者,深度赋能Chiplet产业链,不仅提供工具,更输出STCO设计标准与方法论,成为AI时代系统级智能设计的核心基础设施。

凌峰在回应公司未来战略时强调,芯和始终“围绕着客户的需求走”。“接下来我们会围绕着AI算力与CPU的光互联布局。AI算力跟CPU光是现在绕不过去了,必须得走光。机柜跟机柜之间的互联,肯定是光。所以光的这块的布局我们也在做。”他指出。

这种对“算力+互联”主线的坚定投入,使得芯和不仅提供工具,更输出STCO设计标准与方法论。从Fabless设计、IP、晶圆制造到封装测试,再到存储、液冷、供电等AI基础设施关键领域,芯和正在构建一个连接全产业链的生态操作系统。这种角色蜕变,让芯和跳出EDA工具的红海竞争,迈入系统级生态的蓝海赛道,掌握AI时代半导体产业的话语权。

以STCO为剑,芯和领航国产EDA突围与系统级新大陆

黄仁勋提出的“极限协同设计”,不仅是英伟达的战略方向,更是全球半导体行业的共同趋势。国际EDA三大家早已嗅到变革先机,通过巨额并购布局系统级赛道:新思科技以350亿美元收购Ansys,补齐多物理场仿真短板;楷登电子收购Beta CAE、Hexagon资产,转型智能系统设计;西门子并购Altair,构建完整系统级设计平台。全球EDA行业,正加速脱离“芯片级”红海,拥抱“系统级”蓝海。

面对国际巨头的强势布局,国产EDA如何突围?芯和半导体给出了清晰答案:立足中国产业需求,深耕系统级EDA差异化优势,以STCO为核心,实现换道超车。在品牌发布会现场,面对“如何与国际巨头竞争”的提问,代文亮自信回应:“尽管国际巨头起步早、规模大,但我们有三大核心优势,一是16年底层算法沉淀,华人在物理求解、方程计算领域天赋突出,人才基底扎实;二是与国内客户零距离协作,响应速度远超海外厂商,生态结合更紧密;三是国家大力支持工业软件,我们借助AI算力加速技术迭代,完全有机会实现超越”。

这种自信,源于芯和扎实的技术积累与市场验证。目前,芯和已构建起三大平台、六大解决方案、二十余款EDA工具的全栈体系,覆盖芯片设计、先进封装、PCB板级、高速互连、存储、供电散热等全场景,服务客户涵盖国内头部算力芯片厂商、云服务厂商、封测企业、系统厂商,系统级客户占比达45%,成为国内系统级EDA的领军者之一。针对AI时代的核心需求,芯和推出XAI智能体平台,打造建模、仿真、交互、数据四大智能体,推动“EDA for AI”与“AI for EDA”双向融合。

“AI对EDA的冲击是颠覆性的,未来不再是单一工具售卖,而是全流程解决方案。我们的XAI智能体,就是要打造系统级设计的‘大管家’,实现多模型、多物理场的智能调度”。代文亮强调。

在技术布局上,芯和始终围绕“算力+互联”核心主线,紧跟客户需求迭代升级。从早期28nm厚铜工艺PDK开发,到SiP系统级封装、2.5D/3D IC、Chiplet技术突破,再到AI服务器机柜、光互连、硅光仿真布局,芯和每一步都踩中产业变革节奏。凌峰表示:“我们的战略从未动摇,始终围绕客户需求走。下一步,我们将重点布局光互连、CPU领域,补齐AI生态短板,把九宫格产品线拓展为十六宫格,实现全场景覆盖”。

对于国产EDA的发展路径,芯和用实践证明,不必盲目追随国际巨头的传统路线,系统级EDA是国产EDA的最佳突破口。在先进制程受限、光刻机卡脖子的背景下,系统级优化是弥补制程差距的最有效途径,而芯和在多物理场仿真、STCO方法论、生态整合方面的优势,正好契合国内产业需求,成为国产半导体“非摩尔创新”的核心支撑。

2026年是半导体行业的范式转折年,摩尔定律放缓,AI算力爆发,系统级集成成为行业共识,一场围绕“系统级设计”的产业革命正席卷全球。芯和半导体的全新定位“AI时代的系统设计领航员”,既是芯和的发展方向,也是国产EDA的突围路径。

站在新的历史起点,芯和半导体16年的技术沉淀已化作引领行业的底气,STCO方法论的成熟成为破解产业困局的利器,多物理场耦合引擎的突破筑牢了系统级设计的根基。正如芯和在品牌发布会上的宣言:“以STCO为剑,以多物理场引擎为盾,在AI时代的浩瀚星海中,为半导体产业领航,驶向系统级集成的新大陆”。

未来,随着AI硬件持续迭代,Chiplet、先进封装、光互连、液冷散热等技术全面普及,系统级EDA的市场需求将呈指数级增长,AI硬件领域系统级EDA增速将达行业平均水平的1.5倍,开启百亿美元级新增量市场。芯和半导体作为先行者,将持续深耕STCO领域,完善全栈工具链,深化生态合作,助力国内厂商打造更高效、更可靠、更具成本优势的AI硬件,推动中国半导体产业在AI时代实现跨越式发展。