近日,南方科技大学工学院国家示范性微电子学院潘权教授团队在高速通信与光电集成电路设计领域再次取得重要进展,两个工作发表于国际固态电路会议(IEEE International Solid-State Circuits Conference,ISSCC),一个工作发表于光通信大会(Optical Fiber Communication Conference,OFC)。本次发表的成果包括一款高能效芯粒互连双向传输芯片、一款高能效高速芯粒互连与存储接口芯片,以及一款单片集成高速光电接收机芯片。

此外,潘权教授团队还在集成电路领域知名期刊IEEE Transactions on Circuits and Systems I: Regular Papers(IEEE TCAS-I)上发表了两篇论文,分别报道了一款采用电流复用型模拟前端(AFE)和单环路半速率无参考时钟数据恢复(CDR)的接收机,以及一款具备串扰消除与信号再利用功能的单端接收机前端。其中,关于串扰消除与信号再利用单端接收机前端的论文被IEEE TCAS-I 评选为2026年1月刊亮点文章。

ISSCC被学术界和工业界公认为集成电路设计领域的最高水平会议,享有“芯片奥林匹克大会”之美誉。该会议始于1953年,历来是国际最尖端集成电路技术的首发平台,每年吸引超过3000名来自全球工业界与学术界的参会者,每篇录用的论文均代表了芯片领域最前沿的研究成果。南方科技大学微电子学院潘权课题组今年入选的两篇论文的标题分别为:《A 72Gb/s/pin Single-Ended Simultaneous Bi-Directional Transceiver with C-Peaking Leakage Cancellation and Dual-Loop Hybrid Impedance Calibration for Chiplet Interfaces》和《A 72Gb/s/pin Single-Ended Driver-Cooperative Coded PAM3 Transceiver with Asymmetric Data-Dependent Equalization and Bias-Peaking for Chiplets and Memory Interfaces》,其中后者被评选为亮点论文(Highlighted Papers)。

OFC由美国光学学会(Optica)、IEEE通信协会(ComSoc)和IEEE光子学协会(LEOS)共同举办,是全球光通信领域规模最大、影响力最高的顶级学术与产业盛会。创办于1975年的OFC至今已有超过50年的历史,被公认为光通信行业的风向标,每年吸引超过16,000名专业观众和600余家参展商,是行业发布新品、建立合作、洞察未来的重要平台。

OFC每篇论文都代表着当前光通信领域最重要的发展方向。南方科技大学微电子学院潘权课题组今年有1篇论文入选,标题为:A Monolithic CMOS 28Gb/s PAM-4 Optical Receiver Front-End with Lateral-Enhanced P-Well/N-Well APD for VCSEL-Based Links。该工作被评选为高分论文(Top-Scored),并受到光波技术杂志期刊(Journal of Lightwave Technology,JLT)的邀稿。

图1 ISSCC线下汇报现场照片

论文1:高能效芯粒互连双向传输芯片

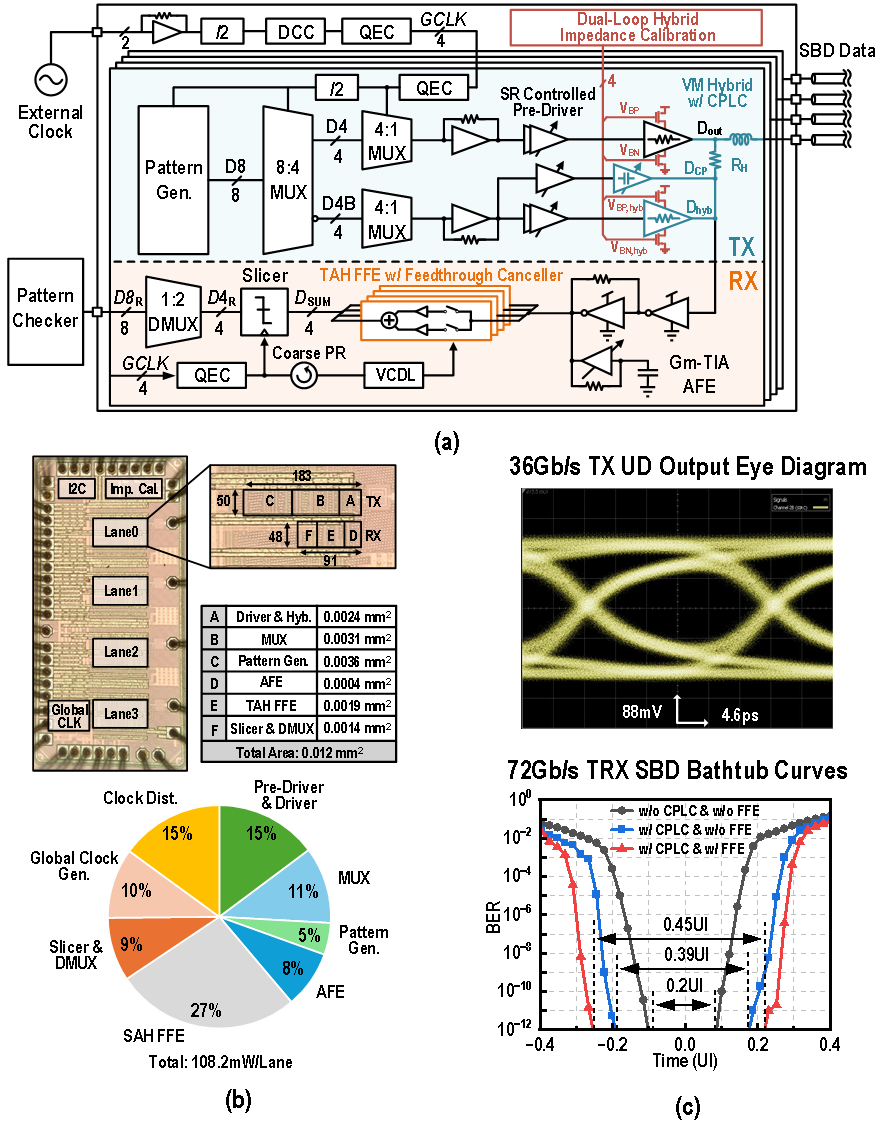

人工智能的爆炸式增长加速了高性能计算和高带宽互连的发展。为了持续提升互联接口的数据吞吐量,双向传输链路通过在信道两端同时发送和接收数据,显示出将系统吞吐量翻倍的潜力。然而,高速双向链路的设计面临着来自出栈信号的高频泄露问题和出入栈信号解耦系数精度问题。针对这两个双向传输链路的技术难点,南方科技大学团队提出了一款72Gb/s/pin的双向传输收发机芯片,其中采用了两项关键技术:一是电容峰化泄露消除技术,通过提取并前馈反相的高频泄漏分量来抑制高频泄露,将高频泄漏幅度从 148mV 降低到 55mV,抑制约63%,实现6倍的眼图开眼幅度的提升;二是双环路阻抗校准技术,使 hybrid 驱动阻抗能够同时跟踪主驱动和 的变化,从而提高出栈信号的消除精度,双环路阻抗校准技术在变化 20% 时将残余误差从最高 60mV 压低到 5mV 以下,降低约 92%。测试结果表明,通过使用所提出的关键技术,结合接收端FFE,该收发机芯片在72Gb/s的数据率下实现了0.45UI的无误码区间,接收端眼高提升至约 244mV,整体能效达到 1.5pJ/b,显示出其在高带宽密度芯粒接口中的竞争力。图2展示了双向传输芯片的电路架构图,功耗分布图以及测试结果。

图2 双向传输芯片的电路架构图,功耗分布图以及测试结果

博士生程旭旭是论文的第一作者,深港微电子学院潘权教授为论文的唯一通讯作者,南方科技大学深港微电子学院为论文的唯一单位,该论文得到了深圳市科技计划项目经费的支持。

论文2:高能效高速芯粒互连与存储接口芯片

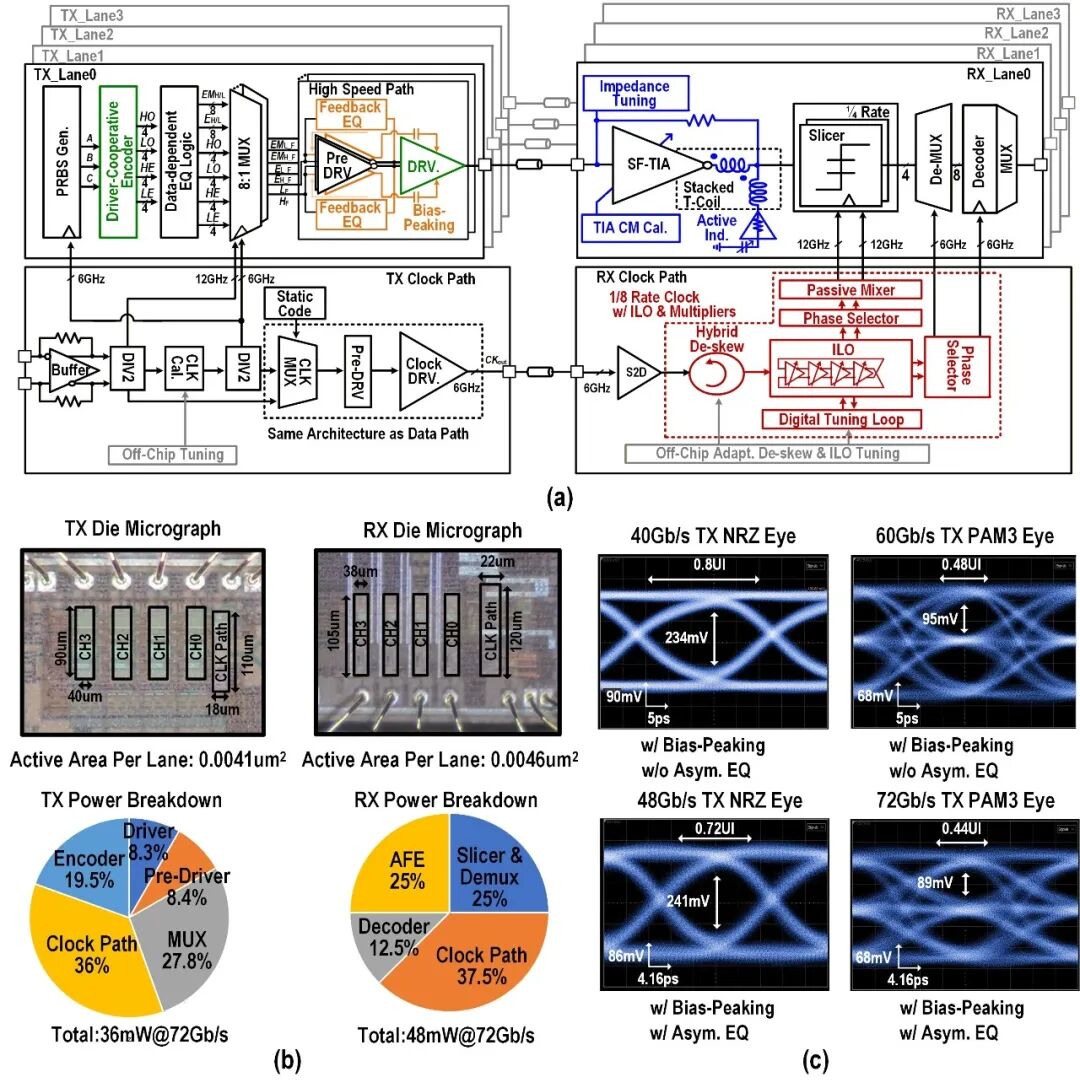

随着人工智能与云计算应用的快速发展,芯粒互连与存储接口需要在有限功耗下实现更高的数据吞吐能力,这推动了高速、低功耗单端有线收发机的持续演进。近年来,PAM3信令因其相较NRZ可提供1.5倍带宽效率、且相较PAM4具有更好的噪声与串扰容限,正成为新一代高密度短距互连的重要候选方案。然而,PAM3信号对码间干扰更为敏感,不同跳变边沿之间的切换抖动也会导致眼宽收缩和信号完整性恶化。针对这一问题,南方科技大学团队提出了一款面向芯粒与存储接口的72Gb/s/pin单端PAM3收发机。该设计采用驱动协同编码与阻抗校准跨阻放大器终端协同优化,在提升信号完整性的同时将信令功耗降低46%;进一步通过预加重非对称数据相关均衡与bias-peaking技术,有效缓解PAM3不同边沿的ISI与切换抖动,将眼图面积分别提升1.9倍和2.8倍。此外,论文还提出了1/8速率前向时钟倍频方案,实现了低功耗、宽范围的去偏斜操作。测试结果表明,该收发机在28nm CMOS工艺下实现了72Gb/s/pin的数据速率,在48Gb/s和72Gb/s下的能效分别达到0.7pJ/b和1.17pJ/b,展现出面向下一代高带宽、低功耗存储与芯粒互连系统的应用潜力。图3展示了存储器接口芯片的电路架构图,功耗分布图以及芯片结果。

图3 存储器接口芯片的电路架构图,芯片图,功耗分布图以及芯片结果

博士后吴泓志是论文的第一作者,深港微电子学院潘权教授为论文的唯一通讯作者,南方科技大学深港微电子学院为论文的唯一单位,该论文得到了国家自然科学基金和获得深圳市科技计划项目经费的支持。

图4 线上汇报实况

论文3:单片集成高速光电接收机芯片

近年来,具有850 nm波长的垂直腔面发射激光器(VCSEL)凭借其高带宽连接特性,在数据中心得到广泛应用。新兴的共封装光学器件(CPOs)采用 VCSEL 技术,可进一步缓解异构集成光模块在可扩展性和功耗方面的挑战。为降低对应光模块的封装复杂度并降低成本,在光接收机前端中,业界采用CMOS片上光电探测器(PD)替代III-V族PD,从而缩短光器件到跨阻放大器电路的传输距离,避免封装寄生效应,实现光器件与专用集成电路(ASIC)的全集成。然而,这种全集成接收系统的主要性能瓶颈仍在于CMOS PD的响应度与带宽,并显著限制系统的速率和误码率。

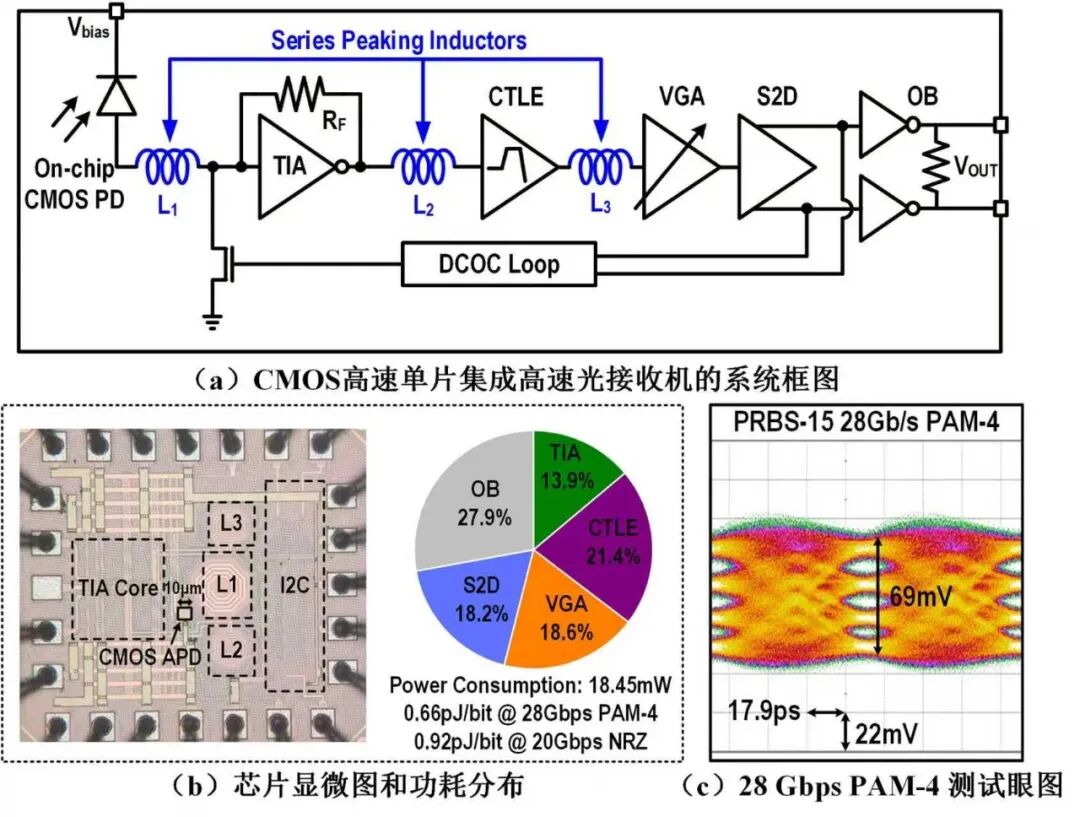

团队从光器件和接收机前端电路入手,基于28-nm CMOS工艺实现了一款面向VCSEL光链路应用的28 Gb/s PAM-4接收机该芯片将PD和跨阻放大器电路集成在一块芯片上,在CMOS工艺上实现了单片集成方案。芯片采用10um×10um受光面积的PD,通过横向插指和浅沟隔离等技术突破了CMOS PD带宽、响应度低等技术瓶颈。同时,在跨阻放大器电路中采用全反相器设计,并插入精心设计的级间电感,显著降低功耗和带内噪声。该研究为低成本、低功耗的高速光接收机设计提供了一种具有实用价值的技术方案,达到了目前国内外CMOS全集成光接收机的最高速率。

图5 高速光电接收机芯片系统架构及芯片性能展示

詹东深为论文的第一作者。詹东深是南科大23级硕士研究生(也是南科大2023届本科毕业生),深港微电子学院潘权教授为论文的唯一通讯作者,南方科技大学深港微电子学院为论文的唯一单位,该论文主要得到了深圳市科技重大专项经费的支持。