近日,中国科学院计算技术研究所处理器芯片全国重点实验室关于大模型容错《STAC: Spatial-Temporal Activation Contextualization for Resilient LLM Inference》和全同态加密(FHE)统一硬件架构的论文《Chimera: A Unified FHE Accelerator with Enhanced Compatibility for TFHE》分别被电子设计自动化领域顶级会议DAC 2026(Design Automation Conference,CCF-A类)接收。

论文

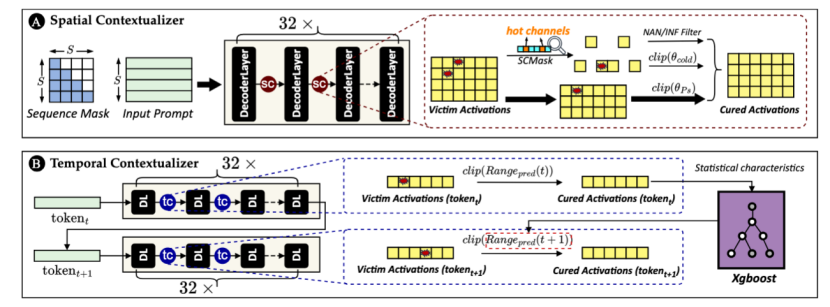

《STAC: Spatial-Temporal Activation Contextualization for Resilient LLM Inference》

该论文第一作者为实验室集成电路课题组博士生张仁刚,通讯作者为刘自臻特别研究助理和李华伟研究员。针对大语言模型(LLM)在安全关键领域部署时面临的软错误威胁,研究团队提出了一种轻量级的时空激活上下文感知容错推理框架STAC。现有低成本防御方法普遍依赖静态阈值,难以适配LLM推理过程中独特的“异常值二分性”问题:高幅值激活既可能是语义表达所必需的功能性异常,也可能源于软错误引发的故障性异常。此外,LLM推理中预填充阶段存在结构化功能异常,解码阶段激活特征随自回归过程发生时间漂移,静态阈值难以同时兼顾两者。为此,团队提出STAC框架,采用“空间感知+时间预测”的解耦机制:预填充阶段利用热点通道掩码区分合法的大数值功能异常,对冷通道严格裁剪;解码阶段提取轻量级统计特征构建XGBoost动态预测器,自适应调整每个token的保护边界。实验表明,STAC在保持无故障精度的同时,将最大可容忍故障率提升至10-6,相比现有低成本防御方法实现10倍可靠性提升,平均延迟开销仅3.85%。该工作基于激活的时空演化特性构建自适应容错机制,在保证效率的同时显著提升系统可靠性,为大语言模型在安全关键场景中的部署提供了可行路径。

论文

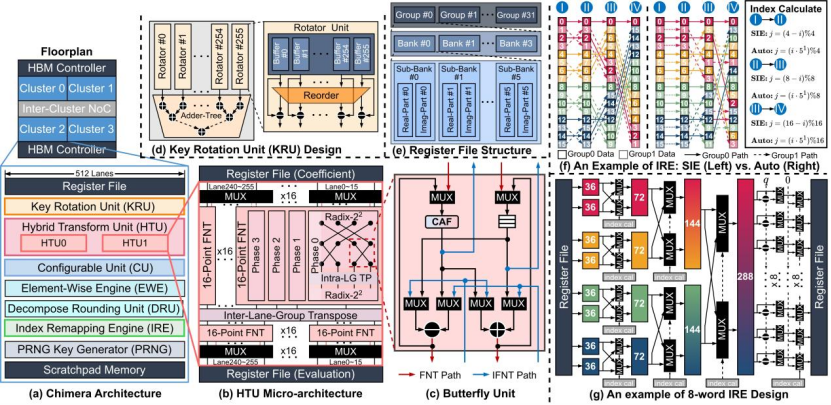

《Chimera: A Unified FHE Accelerator with Enhanced Compatibility for TFHE》

该论文第一作者是实验室在读研究生华腾辉,通讯作者和合作者包括穆嘉楠特别研究助理、叶靖副研究员和李华伟研究员等。为了提升FHE加速器通用性,需要探索统一架构支持不同加密体系。针对现有统一FHE加速器普遍存在兼容性不足、硬件利用率不高以及关键路径性能受限等问题,研究团队提出了新型统一加速器 Chimera。面向多样化 FHE 工作负载在计算模式、数据组织与资源需求上的显著差异,Chimera 从计算架构、功能单元、存储组织以及配置优化等多个层面开展协同设计,在保持统一架构通用性的基础上,显著增强了对复杂逻辑型 FHE 计算的支持能力。与此同时,Chimera 还结合面向系统约束的自动化配置优化方法,能够根据算法参数和硬件配置对运行参数进行协调优化,从而进一步提升整体执行效率与硬件资源利用水平。实验结果表明,与当前先进的统一 FHE 加速器Trinity相比,Chimera 在 TFHE 类工作负载上平均实现 14.64×的性能提升,同时在 CKKS 类工作负载上保持可比性能,且面积开销仅增加 9.6%。该工作展示了统一 FHE 加速器在兼顾通用性、高性能与可扩展性方面的显著潜力,为高效支撑多体系 FHE 应用提供了新的技术路径。

此外,实验室集成电路课题组与北京邮电大学、香港中文大学合作的另一篇关于芯片可靠性评估的论文《ATLAS: Asynchronous Topological Learning for Accurate FIT Prediction via Decoupled Graph Neural Networks》也被本次DAC 2026接收,该论文第一作者来自北京邮电大学,刘自臻特别研究助理为共同通讯作者。

DAC 2026

DAC是电子设计自动化领域的国际顶级会议,主要聚焦集成电路设计、芯片设计方法学、电子系统自动化工具及其软硬件协同优化技术的前沿研究成果。自1964年创办以来,DAC始终引领全球电子设计自动化(EDA)领域的创新与发展,被誉为“芯片设计领域的风向标”,对推动半导体技术、人工智能驱动的设计工具以及高能效计算架构的研究起到了核心推动作用。第63届DAC会议将于2026年7月在美国加利福尼亚州举行,本届会议最终录用率仅为22.3%。

处理器芯片全国重点实验室依托中国科学院计算技术研究所,是中国科学院批准正式启动建设的首批重点实验室之一,并被科技部遴选为首批 20个标杆全国重点实验室,2022年5月开始建设。实验室学术委员会主任为孙凝晖院士,实验室主任为陈云霁研究员。实验室近年来获得了处理器芯片领域首个国家自然科学奖等6项国家级科技奖励;在处理器芯片领域国际顶级会议发表论文的数量长期列居中国第一;在国际上成功开创了深度学习处理器等热门研究方向;直接或间接孵化了总市值数千亿元的国产处理器产业头部企业。

更多信息请访问实验室主页:sklp.ict.ac.cn

处理器芯片全国重点实验室

实验室聚焦处理器芯片的能效墙、设计墙和指令集墙等核心科技问题,系统性发展相关领域的理论、技术、工具和原型芯片,推动处理器芯片科技研究的体系化发展。